依元素FPGA就业加速计划—逻辑设计进阶.第3期

课程背景

FPGA(现场可编程门阵列)被称为“万能芯片”。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了原有可编程器件门电路容量有限的缺点。FPGA可直接面向用户,灵活性和通用性极大,使用方便,实现快捷,能够加速产品上市。

近年来,FPGA技术广泛应用于工业控制、医疗、测试测量、有线通信、无线通信、数据中心、消费类、广播&A/V等领域,并且在人工智能、汽车电子等新兴领域也有广泛和深入的应用,各个行业对FPGA人才的需求越来越大。

本课程是在AMD联合支持下,依元素科技推出的FPGA就业岗前学习进阶课程,基于AMD最新的Vivado设计开发工具,进行快速有效的设计分析和调试;遵循UltraFast设计方法学,通过最优的HDL编码方式,实现时序收敛和功耗优化的高效设计。通过系统的集中学习,使您能够快速适应就业入职所需的FPGA开发技能要求,掌握提升工程开发效率的设计方法,为技能提升和岗位提升打下一定基础。

培训对象

u在校即将毕业学生、本科生/研究生均可

u近期有就业需求的相关FPGA硬件设计和软件开发人员

u软件开发向FPGA硬件开发领域转换的相关技术人员

培训费用

u完全免费

培训时间及形式

u培训日期:2023年9月25号-9月28号

u培训形式:腾讯会议系统-线上

专家团队

AMD官方授权培训合作伙伴 – AMD官方认证培训讲师

课程大纲

时间 | 章节 | 章节内容 |

第1天 | FPGA设计方法-1 | Ø同步设计技术 Ø寄存器复制 Ø使用异步复位的影响 Ø时序例外约束 Ø时钟分组约束 Ø时序概要报告 Ø报告时钟相关性 |

第2天 | FPGA设计方法-2 | Ø生成和封装定制化IP Ø使用IP container Ø使用IP 集成器进行设计 ØVivado设计套件的非项目模式 Ø版本控制系统 ØHLx设计流程 |

第3天 | FPGA设计方法-3 | Ø时序仿真设计和实施 Ø基线技术 Ø使用流水线提升设计性能 Ø推断Xilinx 专用硬件资源 Ø同步电路实现跨时钟域设计 ØI/O 时序概述 Ø时序约束优先权 Ø设计分析和 Floorplanning |

第4天 | FPGA设计方法-4 | ØI/O接口配置 Ø配置模式 Ø动态功耗估算 ØVivado调试工具 Ø在 IP 集成器模块设计中插入调试内核 Ø调试技术 Ø增量编译 ØECO流程 Ø面向低功耗设计的管理技术 |

课程收益

1. 详细了解Vivado设计套件的特性,掌握设计调试的方法及基本技巧;

2. 掌握静态时序分析的方法,能够分析时序异常并采取适合的解决手段;

3. 学会如何最优化HDL编码技术和增量编译技术;

4. 掌握复位技术、同步设计技术、时序收敛技术等以提高设计性能和稳定性。

注册报名

报名链接:http://www.e-elements.com/baoming/bm/id/96.shtml

联系方式

课程咨询:张剑森 18165756976 kenson.zhang@e-elements.com

报名咨询:胡海燕 13814168632 haiyan.hu@e-elements.com

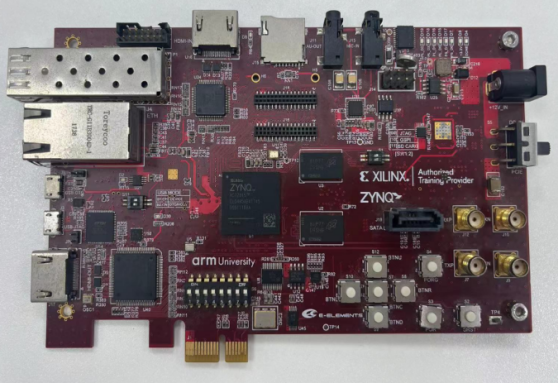

精美礼品

活动结束后将提供答疑和抽奖环节,众多精美礼品等您来分享!

注:依元素科技对培训活动及抽奖享有最终解释权!

依元素Zynq SoC开发板

华为耳机 小米蓝牙音响 充电宝折叠电风扇

注意事项

1. 本培训课程原则上需要具备一定的数字电路基础知识及相关专业课程理论知识,有AMD Xilinx开发工具使用经验更佳,不接受零基础报名。

2.为提高课程质量,依元素科技将要求培训学员必须回复“就业跟踪信息表”。报名学员需明确能够完全配合依元素科技的就业跟踪反馈等工作。

最新活動

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Friday 29, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020

公司新闻

- Thursday 22, 2025

- Monday 12, 2025

- Monday 21, 2025

- Friday 18, 2025

- Thursday 03, 2025

- Friday 07, 2025

- Thursday 13, 2025

- Monday 13, 2025

- Monday 30, 2024

- Wednesday 20, 2024

- Monday 18, 2024

- Wednesday 06, 2024

- Tuesday 29, 2024

- Friday 18, 2024

- Tuesday 14, 2020